QSPICEでは、Verilogで記述されたブロックを作成し、それをシミュレーションすることができる。今回は簡単な加算器ブロックを作成し、Verilogシミュレーションしてみる。

Verilogブロックを作成する手順

QSPICEのHELPで「Ø-Device: Link a Module Defined in a .DLL」にVerilogで作成する手順が記載されている。以下に抜粋を示す。

Second Scenario: Write in Verilog:

Verilog is supported. The overall procedure is

1. Draw a hierarchical block on a schematic.

2. Change the symbol type to Ø(.dll).

3. Add ports for input and outputs.

4. Right click on each port and specify where it is an input or an output.

5. Right click on each port and specify the data type of each port to be boolean, integer, float, etc.

6. Right click on the component and execute menu item Verilog Interface=>Create C++ .DLL Main Template. You should be able to close this without edits. Its job is to convert SPICE data to your typed ports and parameters4.

7. Back at the schematic, right click again on the component and execute menu item Verilog Interface=>Create Verilog Template

8. Implement the function of the device in the body of the template below the comment that reads

このHELPの手順と、公式HPの動画「Using C++ and Verilog in QSPICE」を参考にしながらVerilogシミュレーションを実施する。

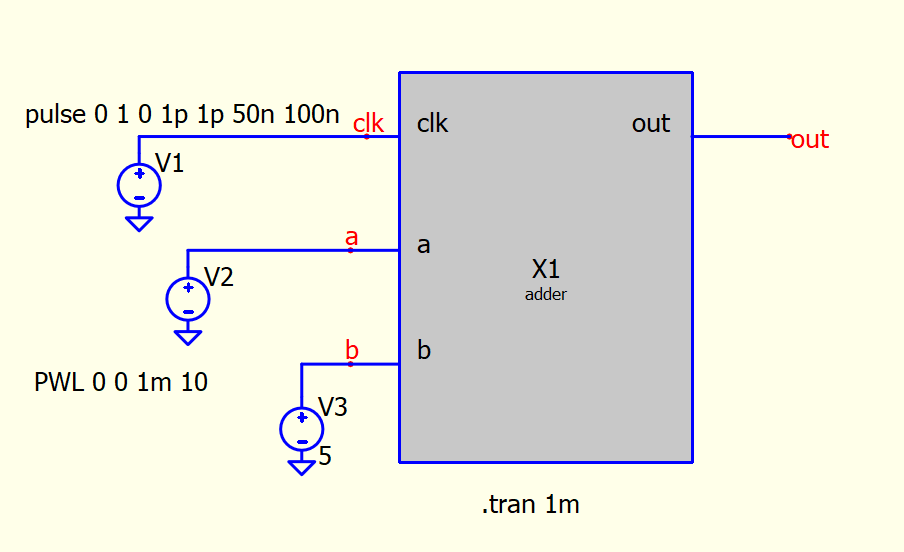

1. 回路図に階層ブロックを描く

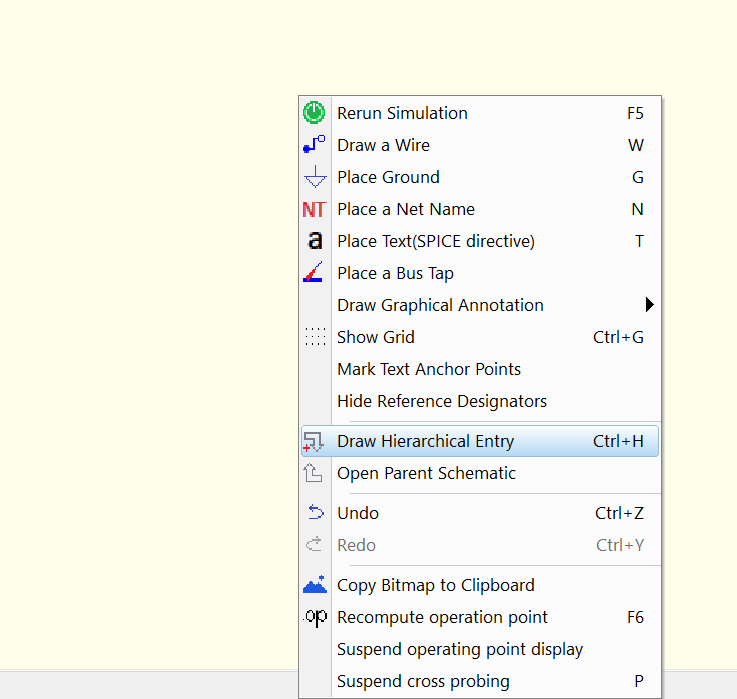

・回路図上で右クリック。「Draw Hierarchical Entry」を選択。

・四角いボックスが書けるようになるので、好きなサイズのボックスを生成。

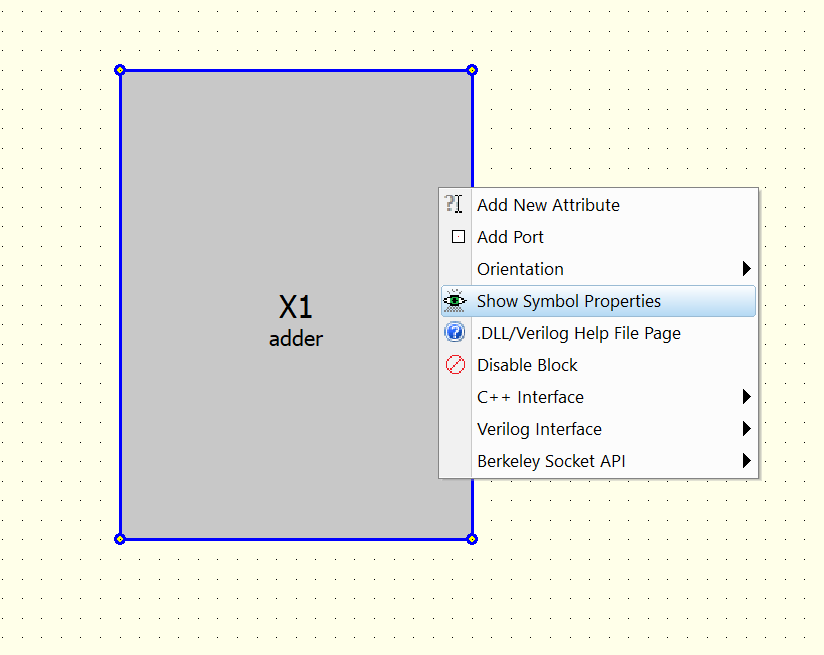

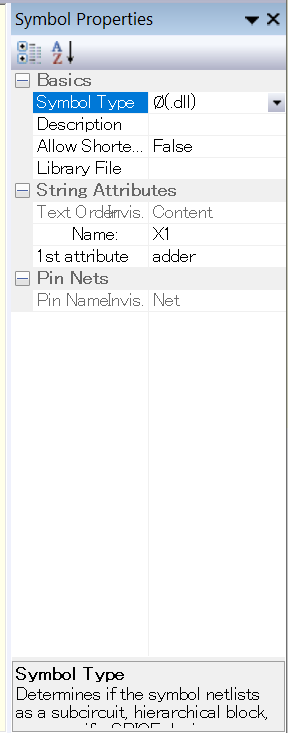

2. シンボルタイプを Ø(.dll) に変更

・ブロック上で右クリック。「Show Symbol Properties」を選択。

・画面右に出てくる「Symbol Properties」の「Symbol Type」を「Φ().dll」に変更。

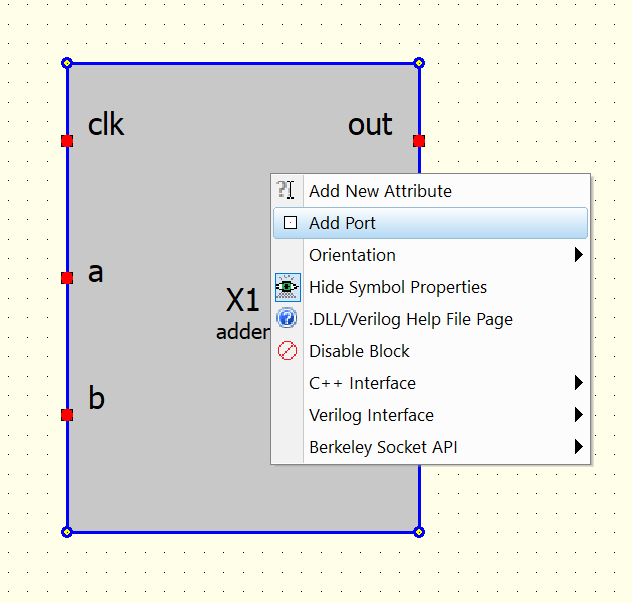

3. 入出力ポートを追加

・ブロック上で右クリック。「Add Port」でポートを追加。

名称はポートをダブルクリックで記入。

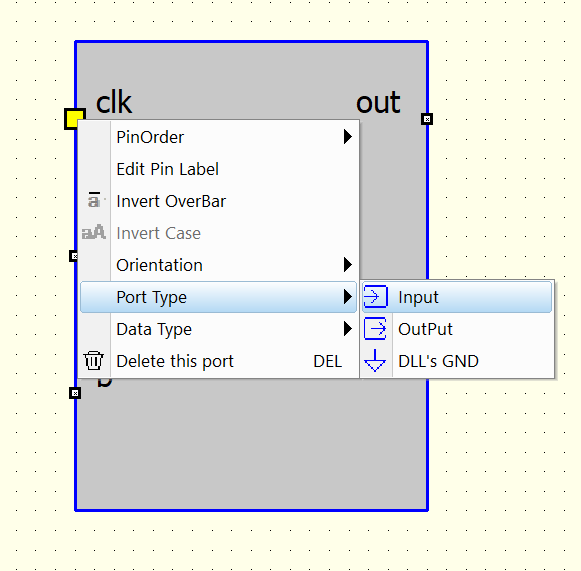

4. 各ポートの入力/出力/を設定

・ポート上で右クリック。「Port Type」でポート設定を実施。

今回は、clk, a, bは入力、outは出力とする。

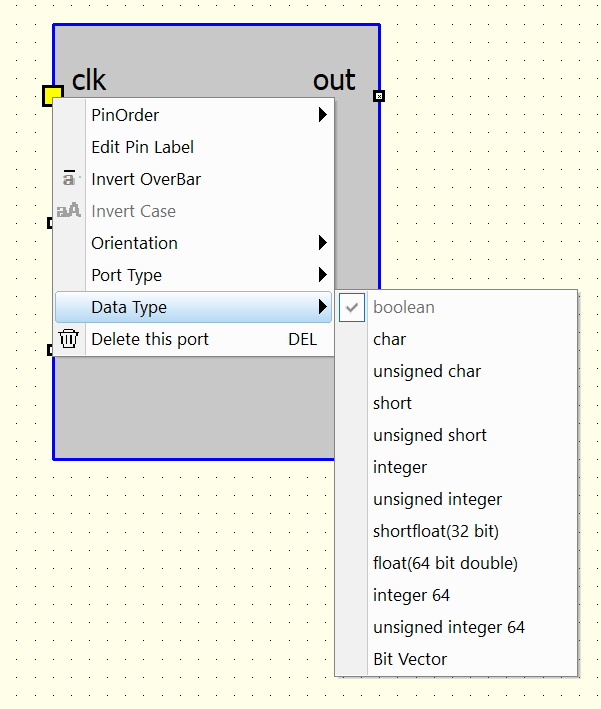

5. 各ポートのデータ型を指定

・ポート上で右クリック。「Data Type」でポートのデータ型を指定。

今回は、clkはboolean、a, b, outはunsigned integer 64とする。

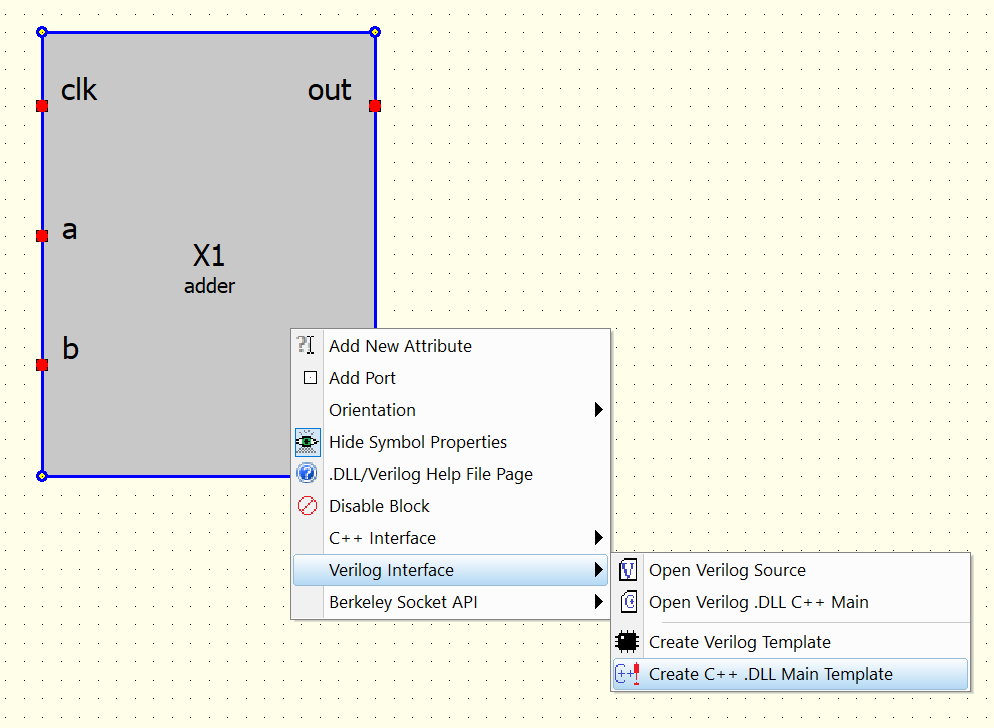

6. Verilog Interface → Create C++ .DLL Main Template を実行

・ブロック上で右クリック。「Verilog Interface」で「Create C++ .DLL Main Template」を実行。

・xxx.cppが開かれるが、これは編集せずにそのまま閉じる。

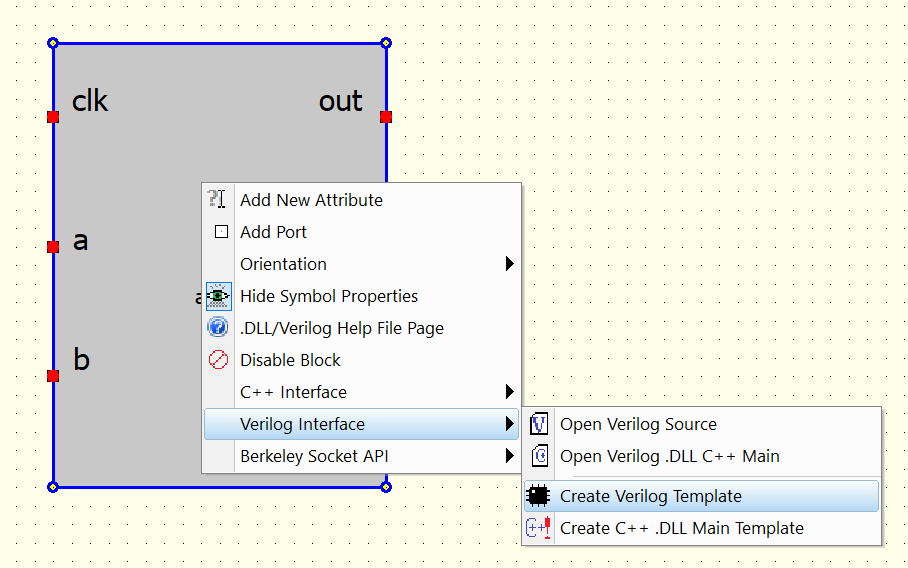

7. Verilog Interface → Create Verilog Template を実行

・ブロック上で右クリック。「Verilog Interface」で「Create Verilog Template」を実行。

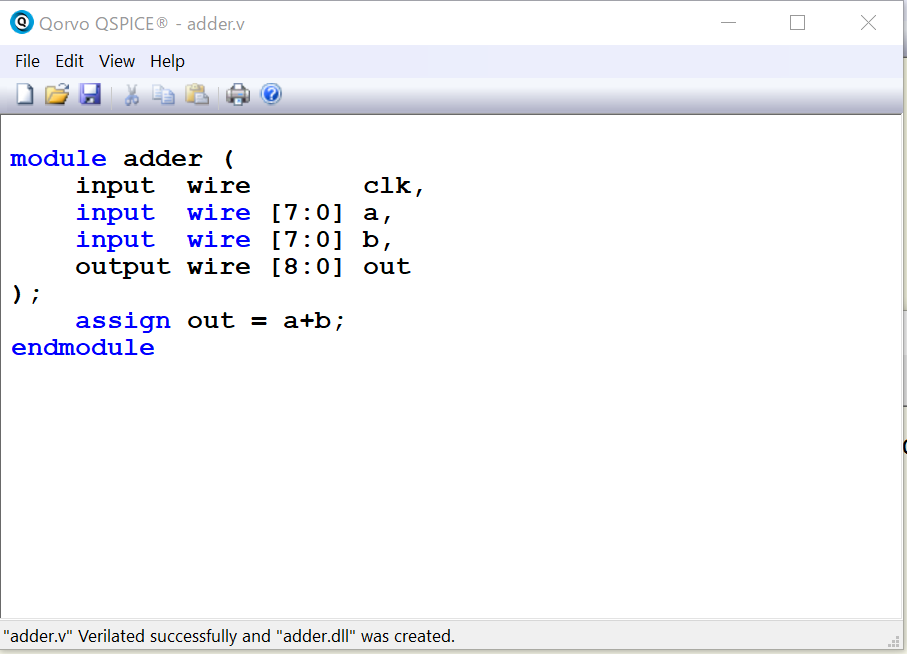

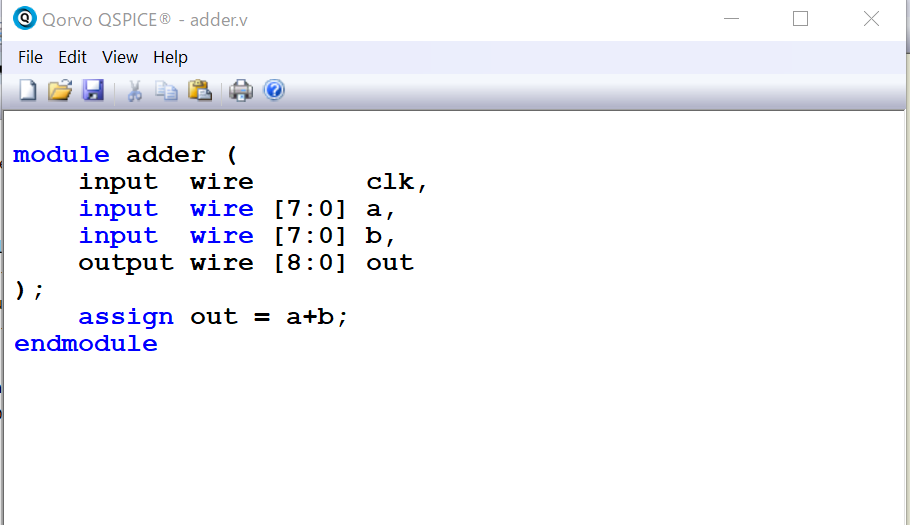

8. 開かれたvファイルにVerilogを記述

・上記7項を実施するとvファイルが開かれるので、自分でVerilogを記述。

今回は、下記のような簡単な加算器(ただの足し算)を記述する。

9. Compile Verilog to C++ を実行

・ファイル上で右クリック。「Compile Verilog to C++」を実行。

一番下に「”xxx.dll” was created」が表示されればOK。